This book takes a more global design perspective in jointly examining the design space at the circuit level as well as at the architectural level. The Clock Design Tool software helps with part selection loop filter design and simulation of timing device solutions.

Cdce L 949 4 Pll Vcxo Clock Synthesizers Ti Mouser

PLL Expert and another one.

. The cosine signal is feed back and multiplied with PLL input signal. Dean shows how to use tis clock design tool to quickly do pll loop filter design. Download ADIsimPLL Key Features Easy-to-use software speeds development process.

Probably in the 600-1500 range. When you enter desired output frequencies and a reference frequency optional the tool provides TI devices to meet the specified requirements divider values and a recommended loop filter to minimize jitter. Hi I have a problem with PLL design software.

To run the program. Simply download the file setup_pll_designexe run it in Windows ie double click on it in Windows Explorer and then follow the setup instructions. These are the ones we recommend.

More Circuit Sage Tools WEB TOOLS. Once the loop is locked the phase. Where you can develop online or download desktop tools including Code Composer Studio CCS.

Ti clock design tool software is used to aid part selection loop filter des. A change from their old routine to be much more powerful and completely web based. Instalation is succesful but problem is with MCR.

I simulate the PLL1 phase noise curves by typing below in clock design tool. Click on the PllDesign icon created during the installation process. Learn how to calculate your gamma and PLL values quickly with the PLLatinum simulator tool.

Learn more about TIs PLL portfolio. The ADIsimPLL design tool is a comprehensive and easy to use PLL synthesizer design and simulation tool. System Requirements Operating System Windows XP Windows XP x64 Windows Vista Windows Vista x64 Windows 7 Windows 7 x64 Microsoft NET Framework.

Separate multiple terms with commas. After the program opens the File - Load Hittite PLL Model File is greyed-out because the model files are not in the directory. Tool Basics The PLL Design Assistant provides a graphical user interface methodology to the design of phase.

All key nonlinear effects that can impact PLL performance can be simulated including phase noise fractional-N spurs and anti-backlash pulse. PLL Design A Phase-Locked Loop PLL is a closed-loop circuit that compares its output phase with the phase of an incoming reference signal and adjusts itself until both are aligned ie the PLL outputs phase is locked to that of the input reference. Uhlik214 on Dec 21 2016.

Eagleware PLL Design. Will be a sure fire hit with both students and their lecturersThis book examines the issue of design of fully-integrated frequency synthesizers suitable for system-on-a-chip SOC processors. When you enter desired output frequencies and a reference frequency optional the tool provides TI devices to meet the specified requirements divider values and a recommended loop filter to minimize jitter.

I am struggling with the PLL phase noise simulation with clock design tool for LMK04828. Of mobile communication transmissions have gained importance PLL and frequency synthesisers have become increasingly topical subjects. The series is an ideal reference for those involved in analogue and mixed-signal design.

ASLK Pro board in antistatic bag Manual schematic and graph paper Wire jumpers transistors and diodes 14 Lab experiments geared toward analog circuit design Lab experiments may be supplemented with SPICE simulation software not included Order Now. Nationals PLL Design Software. Our ADIsimPLL design tool offers support for the latest PLL synthesizers including the new highly integrated ADF4351 PLL for base station and general-purpose applications and the ADRF6850 integrated broadband receiver for satellite applications.

Choose from one of our 12 newsletters that match your product area of interest delivered monthly or. 9900 USD Download the manual PDF 9MB Whats included in the kit. Interested in the latest news and articles about ADI products design tools training and events.

The Clock Design Tool software helps with part selection loop filter design and simulation of timing device solutions. Read Online Fractional Integer N Pll Basics Ti Syntax synthesis semantics simulation and test. TIs WEBENCH Clock Architect online design tool simplifies the design process for a designer using the LMX2592 and LMX2582 as well as TIs other clock and timing devices.

Tool Basics The PLL Design Assistant provides a graphical user interface methodology to the design of phase. RF PLLs synthesizers LMX1204 128-GHz RF buffer multiplier and divider with JESD204BC SYSREF support and phase synchronization LMX2430 30-GHz08-GHz PLLatinum dual high frequency synthesizer for RF personal communications LMX2433 36-GHz17-GHz PLLatinum dual high frequency synthesizer for RF personal communications LMX2434 50-GHz25-GHz. PLL Design Software Version 11 The PLL Design Software is a powerful PLL design tool that enables users to accurately model and analyze performance of all Analog Devices HMC PLLs.

PLL Design Tool. PLL BasicsLoop Filter Design 4 Fujitsu Microelectronics Inc. Automated PLL SynthesisAn automated PLL IC layout compiler and another one.

Kindly can you please take some time to check if there any errors during my simulation. Download Free Fractional Integer N Pll Basics Ti Number 12 in the successful series of Analog Circuit Design provides valuable information and excellent overviews of analogue circuit design CAD and RF systems. Use this icon to run the program or run it by doubling clinking on Hittite_PLL_Design_Toolexe found in CProgram FilesAnalog_Devices_IncHittite_PLL_Design_Toolapplication.

The datasheet says the PN1Hz and PN10KHz of PLL1 as below. Welcome to TIs Development Portal for Embedded Programming. Let PLL input be Let the cosine output of PLL be The input to the Notch filter Where wi Frequency of PLL input signal wo PLL set Frequency at steady state and K Magnitude of PLL input signal.

An intuitive yet rigorous guide to jitter and. Phase Lock Loops and Frequency Synthesis examines the various components that make up the phase lock loop design including oscillators crystal voltage controlled dividers and phase detectors. A Phase-Locked Loop PLL is a closed-loop circuit.

PLL generates two signals One Sine and second Cosine.

Two Microphone Noise Reduction Check With Ti Devices Audio Forum Audio Ti E2e Support Forums

Ti Claims Breakthrough Baw Technology Eetimes

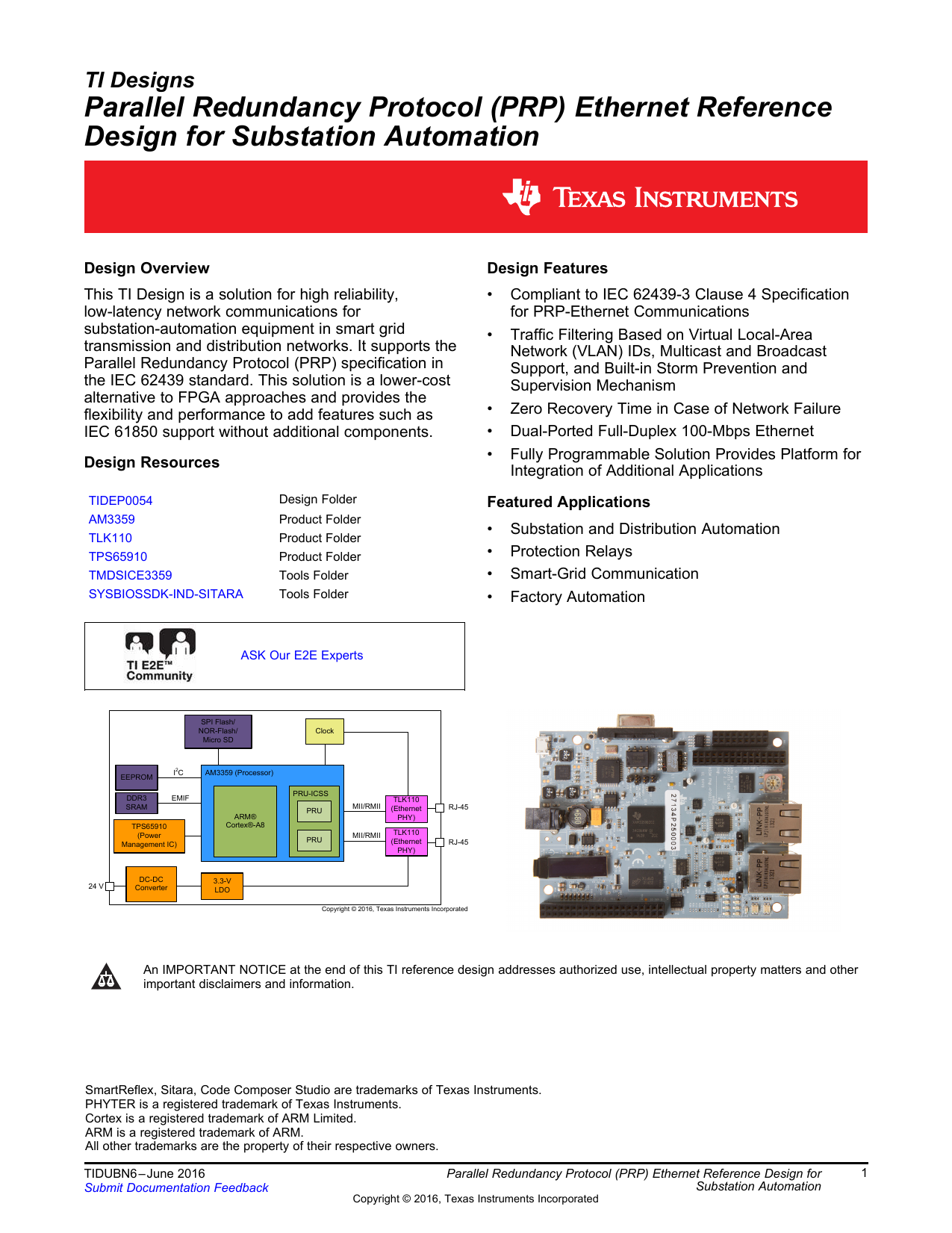

Texas Instruments Parallel Redundancy Protocol Ethernet For Substation Automation Design User Guide Manualzz

Ti Claims Breakthrough Baw Technology Eetimes

Improve Phase Noise By Down Converting The Vco Frequency Planet Analog

Phase Locked Loop Systems Design For Wireless Infrastructure Applications System Wireless Infrastructure

Lm98725 Cds Gain And Pga Data Converters Forum Data Converters Ti E2e Support Forums

0 comments

Post a Comment